AS 1103.8-1986 UDC 003.62:621.3

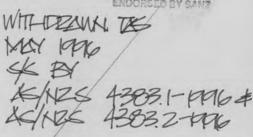

ENDORSEZ BY SANZ

Australian Standard® 1103.8—1986

DIAGRAMS, CHARTS AND TABLES FOR ELECTROTECHNOLOGY

Part 8—GUIDING PRINCIPLES FOR THE PREPARATION OF LOGIC DIAGRAMS

> STANDARDS ASSOCIATION OF AUSTRALIA

> > 12 DEC 1986

MELBOURNE LIBRARY

STANDARDS ASSOCIATION OF AUSTRALIA

Incorporated by Royal Charter

This Australian standard was prepared by Committee TE/13, Symbols, Units and Quantities for Electrotechnology. It was approved on behalf of the Council of the Standards Association of Australia on 15 September 1986 and published on 3 November 1986.

The following interests are represented on Committee TE/13:

Australian Electrical and Electronic Manufacturers Association Ltd

Confederation of Australian Industry

Department of Aviation

Department of Defence

Department of Housing and Construction

Departments of Technical and Further Education, N.S.W., Victoria and South

Australia

Electricity Supply Association of Australia

Institute of Draftsmen, Australia

Institution of Radio and Electronics Engineers, Australia

Melbourne & Metropolitan Board of Works

Queensland Chamber of Mines

Railways of Australia Committee

Royal Melbourne Institute of Technology

Telecom Australia

The Association of Consulting Engineers, Australia

The technical press

Review of Australian Standards. To keep abreast of progress in industry, Australian standards are subject to periodic review and are kept up-to-date by the issue of amendments or new editions as necessary. It is important therefore that standards users ensure that they are in possession of the latest edition, and any amendments thereto.

any amendments thereto.

Full details of all SAA publications will be found in the Catalogue of SAA Publications; this information is supplemented each month by SAA's journal 'The Australian Standard', which subscribing members receive, and which gives details of new publications, new editions and amendments, and of withdrawn standards.

Suggestions for improvements to Australian standards, addressed to the head office of the Association, are welcomed. Notification of any inaccuracy or ambiguity found in an Australian standard should be made without delay in order that the matter may be investigated and appropriate action taken.

# AUSTRALIAN STANDARD

# DIAGRAMS, CHARTS AND TABLES FOR ELECTROTECHNOLOGY Part 8 GUIDING PRINCIPLES FOR THE PREPARATION OF LOGIC DIAGRAMS

AS 1103.8—1986

First published ......1986

### **PREFACE**

This standard was prepared by the Association's Committee on Symbols, Units and Quantities for Electrotechnology. It is one of the AS 1103 series of standards on diagrams, charts and tables which have been prepared under the authority of both the Telecommunications and Electronics and the Electrical Standards Boards.

The AS 1103 series of standards (of which this standard is Part 8) is complementary with the AS 1100 series (Drawing Practice) and the AS 1102 series (Graphical Symbols for Electrotechnology).

For relevant information on matters specific to drawing practice but which are not covered in the AS 1103 series, reference should be made to the AS 1100 series. In addition, reference may also be required to AS 1046, Letter Symbols for Use in Electrotechnology, Part 1, General, and Part 2, Telecommunications and Electronics.

The standards so far published in the AS 1103 series are listed in the SAA Catalogue of Publications.

The purpose of this standard is to provide recommendations for the preparation of logic diagrams. For this reason, it is recommended that the standard be read in conjunction with AS 1102, Graphical Symbols for Electrotechnology, Part 9—Binary Logic Elements, some aspects of which are included in this standard.

During the preparation of this standard, reference was made to IEC 113-7—1981 Diagrams, Charts and Tables for Electrotechnology, Part 7—Preparation of Logic Diagrams. Although this standard is technically similar to IEC 113-7-1981, it also includes additional examples based on Australian practice. However, the polarity indicator logic convention stated herein is not in common use within Australia.

Attention is also drawn to SAA HB8, Understanding Logic Symbols, a new handbook which explains the development of logic symbols depicted in AS 1102, Part 9.

## 3

# **CONTENTS**

|            |                                                    | Pag |  |  |  |  |

|------------|----------------------------------------------------|-----|--|--|--|--|

| 1          | SCOPE                                              | 4   |  |  |  |  |

| 2          | REFERENCED DOCUMENTS                               | 4   |  |  |  |  |

| 3          | DEFINITIONS                                        | 4   |  |  |  |  |

| 4          | GRAPHICAL SYMBOLS                                  | 4   |  |  |  |  |

| 5          | LOGIC CONVENTIONS                                  | 6   |  |  |  |  |

| · 6        | PRESENTATION OF A LOGIC DIAGRAM                    | 6   |  |  |  |  |

| 7          | LAYOUT OF A DIAGRAM                                | 6   |  |  |  |  |

| 8          | UNUSED ELEMENTS AND CONNECTIONS                    | 7   |  |  |  |  |

| 9          | DISTRIBUTED CONNECTIONS                            | 7   |  |  |  |  |

| 10         | SYMBOLS FOR LOGIC ELEMENTS                         | 7   |  |  |  |  |

| 11         | POWER CONNECTIONS                                  | 7   |  |  |  |  |

| 12         | ADDITIONAL INFORMATION (WITHIN OR ADJACENT TO THE  |     |  |  |  |  |

|            | LOGIC SYMBOL)                                      | 7   |  |  |  |  |

| 13         | SIGNAL AND SIGNAL-LINE NAMES                       | 7   |  |  |  |  |

| 14         | USE OF WAVEFORMS                                   | 11  |  |  |  |  |

| 15         | TABULAR INFORMATION                                | 11  |  |  |  |  |

| 16         | REPRESENTATION OF A PIN CONNECTION ACTING AT DIF-  |     |  |  |  |  |

|            | FERENT TIMES AS EITHER AN INPUT OR AN OUTPUT       | 11  |  |  |  |  |

| 17         | INTERACTION OF LOGIC ELEMENTS AND OTHER DEVICES    | 11  |  |  |  |  |

| 18         | EXAMPLES OF LOGIC DIAGRAMS                         | 11  |  |  |  |  |

| APPEŅDICES |                                                    |     |  |  |  |  |

| ,          | A MNEMONICS                                        | 23  |  |  |  |  |

| -          | B GUIDE TO THE APPLICATION OF LOGIC CONVENTIONS IN |     |  |  |  |  |

| •          | LOGIC DIAGRAMS                                     | 26  |  |  |  |  |

|            |                                                    |     |  |  |  |  |

|  | This is a free preview. | Purchase the e | entire publication | at the link below: |

|--|-------------------------|----------------|--------------------|--------------------|

|--|-------------------------|----------------|--------------------|--------------------|

**Product Page**

- Dooking for additional Standards? Visit Intertek Inform Infostore

- Dearn about LexConnect, All Jurisdictions, Standards referenced in Australian legislation